中规模集成电路功能测试仪的设计 集成电路设计中的关键验证环节

在集成电路(IC)设计流程中,功能测试是确保芯片性能、可靠性和符合设计规格的关键环节。随着芯片复杂度提升至中规模(通常指集成度在100至10,000个逻辑门之间),传统的万用表或简单探针已无法满足高效、精准的测试需求。因此,专门针对中规模集成电路的功能测试仪的设计,成为了连接设计仿真与实际应用的重要桥梁。

一、 设计目标与核心功能

中规模IC功能测试仪的核心目标,是在可控环境下,模拟芯片的真实工作条件,施加预设的激励信号,并捕获、分析其输出响应,从而判断芯片功能是否正确。其核心功能包括:

- 激励信号生成:能够产生测试向量(Test Vectors),即一系列输入信号的组合,以覆盖芯片设计规格中的关键功能路径和边界条件。

- 响应捕获与比较:实时采集被测芯片(DUT)的输出引脚信号,并将其与预期的“黄金响应”(Golden Response)进行比对。

- 时序控制与同步:精确控制激励施加与响应采样的时序,确保测试信号满足芯片的建立时间、保持时间等时序要求。

- 故障诊断与定位:当测试失败时,能够提供初步的故障信息,如哪个引脚、在哪个测试向量下出现错误,辅助设计人员进行问题定位。

二、 系统架构设计

一个典型的测试仪硬件系统通常由以下几个模块构成:

- 主控单元:通常采用微控制器(MCU)或现场可编程门阵列(FPGA)作为核心。FPGA因其并行处理能力和可重构性,在中高速测试中更具优势。它负责测试流程控制、测试向量调度、结果分析以及与上位机通信。

- 测试向量存储器:存储大量的测试激励数据和预期响应数据。可采用高速SRAM或利用FPGA内部的Block RAM实现。

- 引脚驱动与接收电路(引脚电子):这是与被测芯片直接接口的关键部分。驱动电路需提供可编程的电压/电流,以产生符合电平标准(如TTL、CMOS)的激励信号。接收电路则需具备高输入阻抗和精确的比较器,以可靠地采集输出信号。对于双向引脚,需要设计方向控制电路。

- 时序发生器:产生精确的时钟和控制信号,协调激励施加、响应采样等操作的时刻。其精度直接影响测试的可靠性和对高速芯片的测试能力。

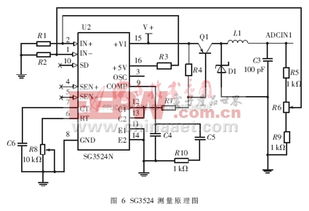

- 电源管理模块:为被测芯片提供稳定、可调、低噪声的供电电压(VDD/VCC)和参考地(GND),并可能集成过流保护功能。

- 通信接口:如USB、以太网或PCIe,用于从上位机下载测试程序、上传测试结果,实现自动化测试。

三、 软件与测试程序开发

测试仪的效能不仅取决于硬件,更依赖于软件系统。软件部分通常包括:

- 上位机软件:提供图形化用户界面(GUI),用于测试项目管理、测试向量编辑(或导入设计仿真工具生成的测试文件)、测试参数配置、测试执行控制以及测试结果的可视化报表生成。

- 测试程序编译器/转换器:将用户编写的测试描述(如用特定语言或波形图)或自动测试模式生成(ATPG)工具产生的测试集,转换为测试仪硬件可执行的底层控制指令和时序数据。

- 故障诊断算法:集成简单的算法,对测试失败的数据进行初步分析,如故障字典查询,帮助缩小故障范围。

四、 设计挑战与考量

设计中规模IC功能测试仪时,需应对以下挑战:

- 引脚数量与密度:中规模IC的引脚数可能从几十到上百个,要求测试仪具备足够的测试通道,且探针或测试插座的设计需考虑引脚间距和布局。

- 测试速度与时序精度:测试仪的运行速度(测试频率)和时序分辨率(如时钟边沿放置精度)必须高于被测芯片的最高工作频率和最小时序裕量要求,否则无法进行有效验证。

- 信号完整性:在高速测试下,传输线效应、串扰、反射等问题会变得突出。需要在PCB设计、接口匹配、电源去耦等方面精心设计,保证测试信号的纯净度。

- 可扩展性与灵活性:为了适应不同封装、不同引脚定义、不同电平标准的芯片,测试仪的硬件接口(如DUT板)和软件配置应具有良好的模块化和可重构性。

- 成本控制:作为研发验证工具,需要在性能、功能和成本之间取得平衡。

五、

中规模集成电路功能测试仪的设计,是一项集成了数字电路设计、模拟电路设计、高速PCB设计、嵌入式软件和上位机软件开发的多学科工程。它不仅是IC设计流程中验证设计正确性的“守门员”,也是进行故障分析、可靠性评估和生产测试准备的必备工具。一个设计精良的功能测试仪,能显著缩短芯片的开发周期,提高设计成功率,为集成电路从设计图纸走向实际应用提供坚实保障。随着集成电路向更大规模、更高速度发展,测试仪的设计也将持续面临新的技术挑战与创新机遇。

如若转载,请注明出处:http://www.yunkudou.com/product/18.html

更新时间:2026-04-16 01:35:35