超高速0.18μm CMOS复接器集成电路设计

随着现代通信系统和数据传输网络对速度与带宽的需求日益增长,高速复接器作为实现多路数据流高效整合与传输的关键模块,其性能至关重要。采用先进的0.18微米互补金属氧化物半导体工艺进行设计,能够在功耗、速度与集成度之间取得优异的平衡。本文将探讨基于0.18μm CMOS工艺的超高速复接器集成电路设计的关键技术与实现方案。

一、 设计目标与挑战

超高速复接器的主要设计目标是在给定工艺下,实现尽可能高的数据吞吐率、低的时序抖动、良好的信号完整性以及低的功耗。在0.18μm CMOS工艺节点下,设计面临的核心挑战包括:

- 速度瓶颈:晶体管的寄生电容和互连线的RC延迟限制了电路的最高工作频率。

- 信号完整性:在GHz级的工作频率下,传输线效应、串扰、电源/地噪声等问题变得突出。

- 功耗管理:高速切换必然带来动态功耗的显著增加,需要进行有效的低功耗设计。

- 时钟分布:为多路选择器提供低抖动、高精度的同步时钟是保证性能的关键。

二、 核心电路架构选择

对于超高速应用,常见的复接器架构包括:

- 基于传输门的选择器:结构简单,但速度受限于传输门的导通电阻和负载电容。

- 电流模逻辑复接器:例如采用CML结构,具有高速、抗干扰能力强的优点,但功耗相对较高,且需要额外的电平转换电路与核心CMOS逻辑接口。

- 基于真单相时钟逻辑的树型结构:通过多级树状结构降低每级负载,适合超高并行度复接,但时钟设计复杂。

在0.18μm CMOS工艺下,为兼顾速度与功耗,一种高效的方案是采用 “预充电-求值”逻辑(如多米诺逻辑)与CML输出级相结合的混合架构。数据选择通路采用优化的多米诺逻辑实现核心的2选1或4选1单元,以获得高速度和较低的动态功耗;最终输出级采用CML驱动器,以提供稳定的高速差分输出,增强驱动能力和抗噪声性能。

三、 关键模块设计与优化

- 高速选择单元设计:

- 采用时钟控制的动态逻辑(多米诺逻辑)作为基本选择单元。通过精心设计上拉网络和下拉网络的晶体管尺寸,优化充电和放电路径,减少关键路径延迟。

- 引入保持器电路以防止动态节点在求值阶段因漏电导致的逻辑错误,同时需谨慎设计其尺寸以避免与下拉管竞争。

- 时钟生成与分布网络:

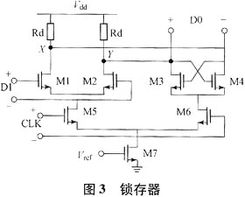

- 采用锁相环或延迟锁相环生成低抖动的高速核心时钟。

- 设计对称的H树或网格状时钟分布网络,确保时钟信号到达各个选择单元的延时偏差最小。

- 在时钟路径上插入缓冲器链并进行尺寸优化,以平衡延迟和驱动能力。

- 输出缓冲器/驱动器设计:

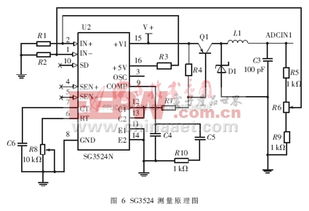

- 采用CML输出级。设计定制的尾电流源和负载电阻,以在满足输出摆幅(通常为200-400mV)的前提下,实现所需的带宽和功耗指标。

- 考虑片外传输线阻抗匹配,通常在输出端集成片上终端电阻(如50Ω)。

- 布局与版图考虑:

- 对称性:对差分路径和关键信号路径进行严格的对称布局,以抵消工艺偏差和降低共模噪声影响。

- 寄生参数控制:使用高层金属(如顶层厚金属)布线关键高速信号线,以减小电阻和线间电容;增加线间距以减少串扰。

- 电源完整性:布置密集的电源和地线网络,并广泛使用去耦电容,尤其是在高速电路模块周围,为瞬态电流提供低阻抗回路。

- 静电防护:所有输入/输出焊盘必须集成符合工艺标准的ESD保护电路,确保芯片可靠性。

四、 设计验证与仿真

在设计流程中,需进行多层次仿真验证:

- 前端仿真:使用电路仿真工具对晶体管级电路进行直流、瞬态和AC分析,验证逻辑功能、建立/保持时间、传输延迟及带宽。

- 后仿:提取包含所有寄生电阻、电容的版图网表进行仿真,这是评估实际芯片性能的关键步骤,尤其关注由寄生效应引起的速度下降和信号畸变。

- 系统级验证:将复接器置于完整的收发链路中进行仿真,验证其在系统环境下的性能。

五、

基于0.18μm CMOS工艺设计超高速复接器,需要综合运用先进的电路技术、精心的版图设计和深入的寄生参数分析。通过采用动态逻辑与电流模逻辑相结合的混合架构,并着力优化时钟网络、输出驱动及电源分布,可以实现在该工艺节点下达到数Gb/s乃至10Gb/s量级的数据吞吐率。此类设计不仅满足了当前高速接口的需求,也为后续更先进工艺下的设计积累了宝贵经验。随着工艺向深亚微米发展,设计挑战将转向更极端的信号完整性和功耗管理问题。

如若转载,请注明出处:http://www.yunkudou.com/product/3.html

更新时间:2026-02-25 08:43:53